## New Insulation Material for Fine-pitch Build-up PWBs

## Hirosaku Nagano

## KANEKA CORPORATION Electronics RD Center 5-1-1, Torikai-Nishi, Settu, Osaka, 566-0072, JAPAN

Phone:+81-726-53-8225, Fax:+81-726-53-8291

E-mail: Hirosaku\_Nagano@kn.kaneka.co.jp, Takashi\_Ito@kn.kaneka.co.jp

The demand of high speed system and down-sizing for many kind of electronic equipment is increasing. To meet this demand, the frequency of CPU tend to be higher, and I/O number of CPU is increasing. From the view point of Build-up PWBs, higher wiring-density is needed for packaging substrate, and lower dielectric constant and dissipation factor are required to the insulation materials for Build-up layer. Kaneka Corporation has developed a new insulation material for Build-up PWBs required high frequency and high density wiring. The new insulation material can be adopted for semi-additive method to fabricate fine pitched circuit, and exhibits high glass transition temperature, low CTE characteristics, low dielectric properties and thickness uniformity of insulation layer.

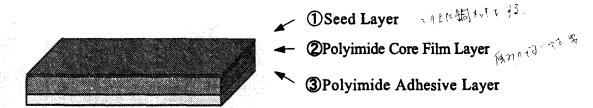

Fig.1 Structure of new insulation material

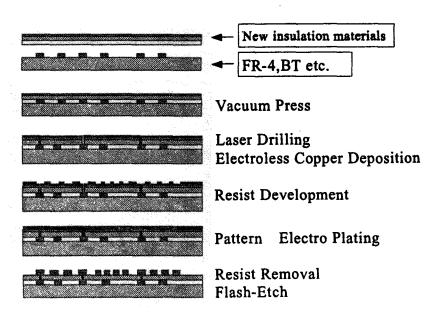

Fig.2 Process flow for Build-up boards manufacturing

Table 2 Specific Properties of the new insulation material

| Properties                                           | Conditions |           |

|------------------------------------------------------|------------|-----------|

| Peel Strength (Seed Layer/Polyimide Core Film Layer) | 180°       | 7N/cm     |

| Peel Strength (Polyimide Adhesive/Copper foil)       | 180°       | 9N/cm     |

| Glass Transition Temp*                               | DMA        | 160℃/310℃ |

| Coefficient of Thermal Expansion*                    | TMA        | 32ppm     |

| Dielectric Constant(ε)                               | 2GHz       | 3.5       |

| Dissipation Factor (tan $\delta$ )                   | 2GHz       | 0.018     |

<sup>\*</sup>shows properties of composite consist from Polyimide Core Film and Polyimide Adhesive Layer

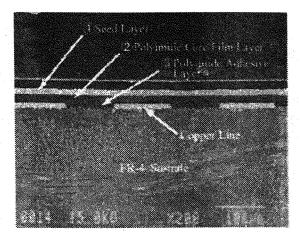

Fig.3 Sectional View After Lamination

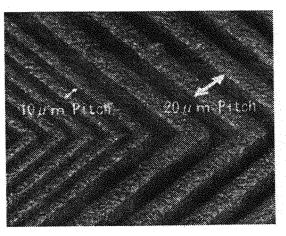

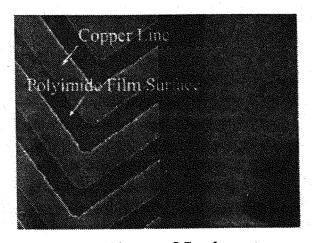

Fig.4 Fine-Piched Circuit Formed on the Core Film.

Fig.5 EDX image of Cu-element Mapping on the Circuit